# The NEMI Roadmap: Integrated Passives Technology and Economics

Joseph P. Dougherty<sup>1</sup>

Materials Research Institute, Penn State University, State College, PA 16802 Tel: 814-865-1638, Fax: 814-865-2326, email <u>JoeDoc@psu.edu</u> Now at the Penn State Applied Research Lab, Electro-optic Science and Technology Center

> John Galvagni AVX Corp.

Larry Marcanti & Rob Sheffield Nortel Networks

> Peter Sandborn University of Maryland

Richard Ulrich University of Arkansas

## ABSTRACT

Passive components, primarily resistors and capacitors, make up the majority of components for electronic circuits. Cost and performance are critical factors while size becomes important in hand held devices. Integrated passive components promise breakthroughs in performance, size, and eventually cost However, poor economic and business conditions have hampered the infrastructure development needed for widespread deployment of integrated passive components. This economic weakness has also made designers more risk evasive in the evaluation of new technologies.

The 2002 NEMI Roadmap finds that performance is the main driver for embedded passives while the lack of design and simulation tools, and test equipment is the primary hindrance to the technology development. In spite of the problems, embedded passive component implementation has been accomplished by manufacturers who have internally developed design tools to circumvent the infrastructure weakness.

The NEMI Roadmap has established new metrics to quantify and compare space savings for comparing discrete passives with integrated passive alternatives. New cost models have allowed us to evaluate the alternative passive component technologies. The space savings, component count savings, board size savings, and conversion cost savings are weighed against higher materials costs. The technical needs and infrastructure needs are spelled out for thin core laminates, ceramic loaded pastes, plated resistors, thin film resistor foils and polymer thick film resistors. Critical gap analyses illustrate the NEMI view of the Integrated Passive Technology's future.

## **INTRODUCTION**

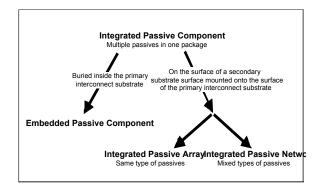

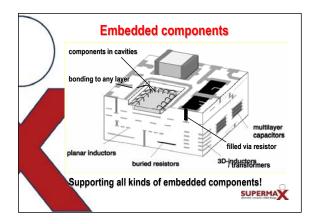

"Passives" usually refer to resistors, capacitors and inductors; but can also include thermistors, varistors, transformers, temperature sensors, and almost any non-switching analog device. The concept of "integrated", "integral", "embedded", "arrayed", or "networked" passives involves manufacturing them as a group in or on a common substrate instead of in their own individual packages.

The different types of passive components are:

- Discrete Components

- Integrated and Embedded Passive Components

- Passive Arrays and Networks

The importance of embedding passive components is seen when the usage rates are charted for portable devices. This category, previously called "hand-held" consists of hand-held, battery-powered products driven by size and weight reduction. In addition to cell phones, this would also involve the palm-size PC (formerly "pocket organizers"), digital cameras, and PCMCIA cards.

| Product             | Number of<br>Passives | Number of<br>Actives | Passives to<br>Actives<br>Ratio |

|---------------------|-----------------------|----------------------|---------------------------------|

| Sony<br>HandyCam    | 1329                  | 43                   | 31:1                            |

| Motorola<br>StarTac | 993                   | 45                   | 22:1                            |

| Nokia 2110          | 432                   | 21                   | 20:1                            |

| Ericsson 338        | 359                   | 25                   | 14:1                            |

Table 1 Active and Passive components for selected handheld products

| Component Distribution<br>Single Board computers |     |  |  |  |

|--------------------------------------------------|-----|--|--|--|

| Component Percentage of Total                    |     |  |  |  |

| Capacitors                                       | 40% |  |  |  |

| Resistors                                        | 33% |  |  |  |

| Miscellaneous Parts                              | 18% |  |  |  |

| Integrated Circuits                              | 5%  |  |  |  |

| Connectors                                       | 4%  |  |  |  |

Table 2 Active and Passive component percentages for single board computers.

Statistically passive components account for:

- 30% of the solder joints

- 40% of the board area

- up to 90% of the placement time

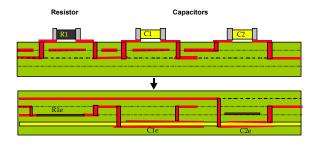

The SMT discrete components usually surround integrated circuit (IC) chips. A one to one replacement of embedded for discrete would use the singulated construction shown in figure 1.

Figure 1. A Depiction of the Embedded Passive <u>Singulated</u> construction. for both the resistor and the capacitor.

For both the resistor and capacitor, there are several choices of techniques. As an example, for the resistor, one can use a subtractive process, requiring an entire layer be inserted and patterned, or an

additive process, where a metal film or a filled polymer can be applied in a particular surface area, then trimmed to tolerance..

Figure 2 Trimmed Metal Thin film

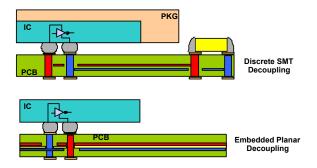

An alternative process can use a distributed planar construction where the entire plane between power and ground is used as a capacitor.

Figure 3. The <u>distributed planar</u> construction for embedded decoupling capacitance.

In the case of figure 3, a single decoupling capacitor covers the entire plane. Each capacitive decoupling requirement is met by dropping down a via to the same power-ground electrode plane. Since the via is a low inductance path, high speed performance can be obtained. A hierarchy of integrated components is shown in figure 4.

Figure 4. . A hierarchy of integrated components.

Portable Devices: The cell phone market continues to be the volume driver for passives, with hundreds of millions required per year. The future growth though, may be different. As predicted in the last roadmap by this emulator, there is a bifurcation of the market taking place. A smaller portion will continue to grow in technology, using GPS-E911 circuitry, and other passives-loaded options; such as more IC's, more memory, and more passives. 3G phones will have more computer functions. Bluetooth, is still evolving, is anticipated to grow. It is anticipated that the passive configurations of 0201 and embedded will concentrate in the proprietary modules. These increases in functionality are limiting the further shrinkage of the overall phone and creating more problems with thermal dissipation. This will impact the ability of power supply manufacturers to meet future needs

On the negative side, some trends, including the use of FPGAs and a trend toward direct conversion of the RF architecture, eliminating IF, will cause a significant reduction in the use of passives This picture however, no longer applies to the bulk of the market, but only to the so-called "High Tier" which will represent 25% of the volume at most. The other 75% will be under huge price pressures, with the general aim of getting the <u>total</u> Bill of Materials to less then \$30.

#### How much can be embedded and is it economical?

Capacitance values are our main concern, as they directly determine space. Resistors, for the most part, can be more flexible, their size mainly affecting the power capability, but capacitance is an areadependent entity. The set of parts in Table 3 is heavily weighted toward the low end of the capacitance values. That is to be typical for the RF types of circuitry common in many portable devices. All of the capacitors < 0.1nF are possible to replace with embedded. The following Table 5 is a selection of parameters from the Portable emulator forecast matrix, which may have some effect on passive planning

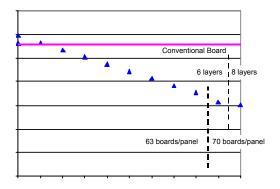

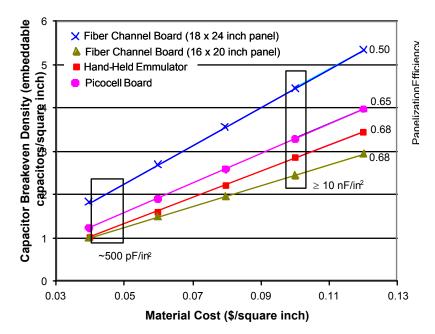

The break even costs have been evaluated by Peter Sandborn<sup>1</sup> and are shown in figure 5, where it is seen that the relative system cost for embedded capacitors is lower when about 15% of the embeddable capacitors are replaced.

Figure 5. Relative Cost analysis

The economics are a strong function of the cost of the replacement materials and their capacitance /area. This is seen in figure 6 where breakeven occurs at between 2 and 5 capacitors/in<sup>2</sup>. The portable (handheld) NEMI emulator has more than 23 capacitors/in<sup>2</sup> that can be embedded. This economic argument and the improved performance due to low inductance is the reason that recently Motorola has introduced embedded capacitors coupled with Microvia technology<sup>2</sup>. This process is called "mezzanine" construction.

|         | Capacitor Value Spectrum for Portable Devices |        |        |        |         |  |  |

|---------|-----------------------------------------------|--------|--------|--------|---------|--|--|

| <100 pF | 0.1 nF                                        | 1.0 nF | 10 nF  | 0.1 uF | 5.4 × F |  |  |

|         | 1.0 nF                                        | 10 nF  | 100 nF | 1 uF   | >1 uF   |  |  |

| 44%     | 14%                                           | 12%    | 19%    | 2%     | 9%      |  |  |

|         | Resistor Value Spectrum for Portable Devices  |        |        |        |         |  |  |

| <100 Ω  | 0.1 kΩ                                        | 1 kΩ   | 10 kΩ  | 100 KΩ |         |  |  |

|         | 1.0 kΩ                                        | 10 kΩ  | 100 KΩ | 1 MΩ   | >1 MΩ   |  |  |

| 13%     | 44%                                           | 12%    | 26%    | 3%     | 2%      |  |  |

Table 3: Passive Components Value Distribution for Portable Devices

| First Year of Significant<br>Production      | Metric            | 2003             | 2005             | 2007      | 2013      |

|----------------------------------------------|-------------------|------------------|------------------|-----------|-----------|

| Board Assembly<br>(Conversion) Cost          | ¢ per I/O         | 0.5              | 0.45             | 0.4       | 0. 3      |

| Package I/O Pitch<br>(Perimeter)             | mm                | 0.5              | 0.5              | 0.5       | 0.5       |

| Package I/O Pitch (Area<br>Array)            | mm                | 0.5              | 0.5              | 0.5       | 0.5       |

| Substrate Lines and Spaces                   | microns           | 75               | 65               | 65        | 35        |

| Substrate Pad Diameter*                      | microns           | 225              | 200              | 175       | 125       |

| Components per cm <sup>2</sup>               | #/cm <sup>2</sup> | 15               | 15               | 17        | 25        |

| Max Components per cm <sup>2</sup>           | #/cm <sup>2</sup> | 50               | 55               | 60        | 25        |

| Frequency on Board                           | MHz               | 150              | 250              | 300       | 400       |

| Solder                                       | Composition       | Lead / Lead-Free | Lead-Free / Lead | Lead-Free | Lead-Free |

| RF Components Thickness                      | mm                | 2.5              | 1.5              | 1.5, MEMS | 1.5, MEMS |

| Passive Components                           |                   | 0201             | 0201             | Embedded  | Embedded  |

| Product Introduction Cycle<br>Time, Platform | Months            | 10               | 9                | 8         | 6         |

| Product Introduction Cycle<br>Time, Spin     | Months            | 4                | 3                | 2         | 1         |

**Table 4.** Projected needs for the Portable emulator

Figure 6 - Bypass capacitor breakeven densities in capacitors/in<sup>2</sup> as a function of dielectric material capacitance and replacement costs, and panel use efficiency.

Only single layer substitution is considered in this plot.

The actual embeddable capacitor densities are :

Fiber Channel Board – 1.12 caps/in<sup>2</sup>, Picocell Board – 2.76 caps/in<sup>2</sup>, NEMI Hand Held Emulator – 23.44 caps/in<sup>2</sup>.

#### **Internal Driving Forces:**

Within the component industry itself there is always the classic driving forces of Price, Performance and Infrastructure. These are the data in Table 4 which tabulated the expected Product Emulator requirements. The cost issues have to be addressed on an application specific basis; this was done by Sandborn in the Advanced Embedded Passives Technology (AEPT) program. The materials and manufacturing infrastructure is still not large enough to support widespread use of embedded passives. In addition, there are some problems that need to be addressed. These are discussed next.

#### Materials & Manufacturing Needs for Integrated Passives

Embedded passive materials offer improved board performance at high frequencies and the possibility of reducing board size or increasing board functionality by removing surface mount components. There has been significant progress in the development of several new materials, including:

- Very thin core laminates, some with ceramic-loaded dielectrics

- Ceramic and ceramic-loaded capacitor pastes

- Plated resistors

- Deposited thin-film resistor foils

- Polymer thick-film resistor pastes

Although some of these are or soon will be commercially available, several technology improvements must take place to enable this technology to meet cost, tolerance, and high-speed performance objectives.

There are many technological needs in integrated passive development. Five of the most important are listed below:

Determine the Amount and Distribution of Capacitance Required for Decoupling with Integrated Capacitors. The much lower inductance of integrated decoupling capacitors enables less total capacitance to be used, since surface mount decoupling strategies typically string excess capacitance in parallel in order to lower the overall inductance. How much less and how the total decoupling capacitance (integrated near the chip and as SM further away) should be optimally arranged is not known. Achieve a manufacturable  $0.3\mu$ F/cm2 for organic substrates: This might be accomplished by lowering the processing temperatures for ferroelectric dielectrics, decreasing the thickness of paraelectric dielectrics, or embedding high-k materials after they are formed.

**Develop High**  $\Omega$ /square Thin film resistor **Materials:** There are now good materials for low range (100 - 300  $\Omega$ /sq.) such as TaNx, CrSi, and NiCr. However, there is a need for 1000 to 10,000  $\Omega$ /sq. and no easily-manufactured materials are available at this time.

**Solve the Problems with Polymer Thick film Resistors:** The mechanisms of value drift and reliability are well understood. Once they are solved, the low price and equipment requirements of PTF resistor material would make it very attractive for integration relative to thin film materials.

**Determine Yield and Reliability of Large-Area Thin Film Embedded Capacitors:** High-value integrated capacitors might have large areas of over 1 cm<sup>2</sup>. These large aspect ratio films might be prone to mechanical damage from CTE mismatch, bending, and ESD. Improved reliability is often cited as a reason for integrating passives, but new failure mechanisms will certainly be present in the new technology

#### Need for Design Tools:

Companies that have implemented embedded components have be forced to develop their own design tools. The design tool companies to date appear to be lagging the technology rather than leading. They appear to be waiting for the technology to take off before they get actively involved. This will impede a large scale adoption of the technology. Industry that has the need to design for high speed in copper will be required to continue to manually design and place embedded component.

Recently a Danish Company (DDE USA Inc) has been marketing design tool software that can include embedded capacitors resistors and inductors (figure 7). This may end the "chicken and egg" stalemate that has existed for the last few years.

Figure 7. Newly marketed embedded design software

### **Performance Drivers:**

The implementation of the "mezzanine" capacitors is a demonstration of both performance drivers, size and speed. The high speed performance is accomplished through the lower inductance of the via connection compared to conventional SMT components. However, SMT technology has been addressing the same low inductance question.

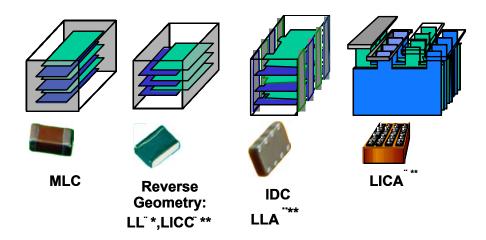

Lower Series inductance: The standard ceramic capacitor has an ESL (equivalent series inductance) of 500 to >1000 pH. Size reduction from 0805, 0603, 0402, to 0201 has played a role in reducing that value. Further reductions in ESL have been accomplished by a number of ceramic capacitor suppliers by careful attention to the current/charge flow within the multilayer capacitor . This has resulted in some unusual geometries as seen in Figure 8. The consequence of these geometrical optimizations is that SMD components offer an increasingly wide array of low inductance options, albeit at a cost premium. For decoupling of high speed microprocessors using close attach capacitors, the loop or trace inductance in the PCB becomes a significant portion of the total inductance. This is placing pressure on designs which will allow reduction of this loop inductance by embedding in the PCB. The maturation of ceramic multilayer technology and the reduction of operating voltages to < 6 volts has allowed for construction of thinner dielectric layers and higher layer counts which result in much higher capacitance values for a given footprint. These factors encourage the embedding, or close attach, of ceramic multilayer capacitors in critical decoupling applications. Some concern has also been expressed that the ESR has become so low,

that undesired "Ringing" and EMI problems have arisen, so some effort is being expended in designing higher resistance back into the devices.

# External Drivers and a Semiconductor Paradigm Shift:

Many passives are used to implement the electrical requirements of the interconnects between integrated circuits. We are all familiar with the picture of a printed circuit board with a few large digital ICs surrounded by passive components like a queen bee tended by the workers.

The semiconductor promises of "System on a Chip" have yet to be realized. However, there is a paradigm shift occurring from Generic ICs to Generic Programmable Logic. I call this "System Within a Chip". Programmable Logic Gate Arrays, (FPGA) can enable a electrical designer to implement memory <u>and</u> microprocessor functions all <u>within a single FPGA chip</u>.

For the first time fewer attending components will be needed to implement almost all the non-analog electrical functions in a single semiconductor device. The applications most likely to be implemented are cell phones and small intelligent controllers in appliances and set-top boxes.

The world economic problems have delayed the explosive cell growth predicted in the past. This may allow alternative FPGA technologies to be implemented, and reduce the projected capacitor usage predicted in the past.

Ironically, just like the embedded passives, this change to the use of FPGAs is being hampered by lack of infrastructure and design software.

#### Gap Analysis and Summary:

After examining many pieces of data, the NEMI Roadmap provides a gap analysis. These are given below in Tables 5-10. No analysis is needed for discrete components, since the only issue is placement difficulties with 0201 size components. In our analyses we have used green to indicate that the critical problems are solved. Yellow indicates that the situation is possible but marginal. Red indicates a critical gap in the technology.

Figure 8. Evolution of low inductance MLCs. (" LL" and "LLA" are trademarks of Murata, and "LICC" and "LICA" are trademarks of AVX).

### GAP ANALYSIS TABLES

| Technology                    | Area of<br>Concern | 2001                          | 2003                            | 2005                        | 2007                                          | 2013                                                 |

|-------------------------------|--------------------|-------------------------------|---------------------------------|-----------------------------|-----------------------------------------------|------------------------------------------------------|

| Integrated Passive<br>Devices |                    | Demonstrable                  | Demonstrable                    | Meets<br>Requirements       | Meets<br>Requirements                         | Meets<br>Requirements                                |

|                               | Manufacturing      | Acceptable Yields             | Acceptable Yields               | Existing<br>Infrastructures | Available<br>Cost-Effective<br>Infrastructure | Available<br>Cost-Effective<br>Infrastructure        |

|                               | Design and Test    | Demonstrable                  | Demonstrable                    | Common Practice             | Widespread                                    | Widespread                                           |

|                               | Cost               | Acceptable                    | Competative                     | Cost Savings                | Cost Savings                                  | Cost Savings                                         |

|                               | Availability       | Few Suppliers<br>No Standards | More Suppliers<br>IPC Standards | Existing<br>Infrastructures | Available<br>Cost-Effective<br>Infrastructure | Standard Parts<br>Available from<br>Multiple Sources |

Table 5, GAP Analysis for the Integrated Passive Devices : Integrated Passive Devices are becoming more accepted as more suppliers emerge. The products continue to improve, but no technical challenges remain.

| Technology                        | Area of<br>Concern | 2001                          | 2003                            | 2005                        | 2007                                          | 2013                                                 |

|-----------------------------------|--------------------|-------------------------------|---------------------------------|-----------------------------|-----------------------------------------------|------------------------------------------------------|

| Distributed Planar<br>Capacitance | Materials          | Demonstrable                  | Meets<br>Requirements           | Meets<br>Requirements       | Meets<br>Requirements                         | Meets<br>Requirements                                |

|                                   | Manufacturing      | Low Yields                    | Acceptable Yields               | Existing<br>Infrastructures | Available<br>Cost-Effective<br>Infrastructure | Available<br>Cost-Effective<br>Infrastructure        |

|                                   | Design and Test    | Demonstrable                  | Demonstrable                    | Demonstrable                | Common Practice                               | Widespread                                           |

|                                   | Cost               | High                          | Acceptable                      | Competative                 | Cost Savings                                  | Cost Savings                                         |

|                                   | Availability       | Few Suppliers<br>No Standards | More Suppliers<br>IPC Standards | Existing<br>Infrastructures | Available<br>Cost-Effective<br>Infrastructure | Standard Parts<br>Available from<br>Multiple Sources |

**Table 6, Gap Analysis for Distributed Planar Capacitance:** Distributed Planar capacitance is showing yield improvements in manufacturing, but there still is a gap in design and test. No major design company plans to include planar decoupling capacitance up to 2005. The companies that use this technology have developed their own internal design tools and test procedures.

| Technology                           | Area of<br>Concern | 2001                                               | 2003                            | 2005                                                 | 2007                                          | 2013                                                 |

|--------------------------------------|--------------------|----------------------------------------------------|---------------------------------|------------------------------------------------------|-----------------------------------------------|------------------------------------------------------|

| Embedded<br>Singulated<br>Capacitors | Materials          | Do Not meet<br>Requirements<br>(Values, tolerance) | Demonstrable                    | Meets Low Freq.<br>Requirements                      | Meets<br>Requirements                         | Meets<br>Requirements                                |

|                                      | Manufacturing      | Low Yields                                         | Acceptable Yields               | Acceptable Yields<br>(Preliminary<br>Infrastructure) | Existing<br>Infrastructure                    | Available<br>Cost-Effective<br>Infrastructure        |

|                                      | Design and Test    | Demonstrable                                       | Demonstrable                    | Demonstrable                                         | Common Practice                               | Widespread                                           |

|                                      | Cost               | High                                               | Acceptable                      | Competative                                          | Cost Savings                                  | Cost Savings                                         |

|                                      | Availability       | Few Suppliers<br>No Standards                      | More Suppliers<br>IPC Standards | Existing<br>Infrastructures                          | Available<br>Cost-Effective<br>Infrastructure | Standard Parts<br>Available from<br>Multiple Sources |

**Table 7, GAP Analysis for Embedded Singulated Capacitance:** Embedded singulated capacitors have recently solved some of the materials problems, however manufacturing know-how is not widely known and the design and test problems are even more serious than for the planar decoupling capacitance.

| Technology                            | Area of<br>Concern | 2001                                           | 2003                                           | 2005                            | 2007                                          | 2013                                                 |

|---------------------------------------|--------------------|------------------------------------------------|------------------------------------------------|---------------------------------|-----------------------------------------------|------------------------------------------------------|

| Embedded<br>Resistors*                | Materials          | Meets<br>Requirements                          | Meets<br>Requirements                          | Meets<br>Requirements           | Meets<br>Requirements                         | Meets<br>Requirements                                |

| *Subtractive Metal<br>Film Technology | Manufacturing      | Acceptable Yields<br>Minimal<br>Infrastructure | Acceptable Yields<br>Minimal<br>Infrastructure | Existing<br>Infrastructures     | Available<br>Cost-Effective<br>Infrastructure | Available<br>Cost-Effective<br>Infrastructure        |

|                                       | Design and Test    | Demonstrable                                   | Demonstrable                                   | Demonstrable                    | Common Practice                               | Widespread                                           |

|                                       | Cost               | High                                           | Acceptable                                     | Competative                     | Cost Savings                                  | Cost Savings                                         |

|                                       | Availability       | Few Suppliers<br>No Standards                  | Few Suppliers<br>No Standards                  | More Suppliers<br>IPC Standards | Available<br>Cost-Effective<br>Infrastructure | Standard Parts<br>Available from<br>Multiple Sources |

**Table 8, GAP Analysis for Embedded Resistors: SUBTRACTIVE PROCESS:** Although no material or manufacturing issues remain unsolved, embedded resistors made by the subtractive process suffer from lack of suppliers and a poor understanding of the cost structure for implementation.

| Technology                        | Area of<br>Concern | 2001                          | 2003                                           | 2005                                          | 2007                                          | 2013                                                 |

|-----------------------------------|--------------------|-------------------------------|------------------------------------------------|-----------------------------------------------|-----------------------------------------------|------------------------------------------------------|

| Embedded<br>Resistors*            | Materials          | Demonstrable                  | Meets<br>Requirements                          | Meets<br>Requirements                         | Meets<br>Requirements                         | Meets<br>Requirements                                |

| *Polymer Thick<br>Film Technology | Manufacturing      | Low Yields                    | Acceptable Yields<br>Minimal<br>Infrastructure | Existing<br>Infrastructures                   | Available<br>Cost-Effective<br>Infrastructure | Available<br>Cost-Effective<br>Infrastructure        |

|                                   | Design and Test    | Demonstrable                  | Demonstrable                                   | Demonstrable                                  | Common Practice                               | Widespread                                           |

|                                   | Cost               | High                          | Acceptable                                     | Competative                                   | Cost Savings                                  | Cost Savings                                         |

|                                   | Availability       | Few Suppliers<br>No Standards | More Suppliers<br>IPC Standards                | Available<br>Cost-Effective<br>Infrastructure | Available<br>Cost-Effective<br>Infrastructure | Standard Parts<br>Available from<br>Multiple Sources |

**Table 15, GAP Analysis for Embedded Resistors: ADDITIVE PROCESS:** Recent progress in a NIST Advanced Technology Program (AEPT) has solved many of the materials problems with the technology. A manufacturing infrastructure, and the same design and test problems as the singulated capacitors, remain as gaps.

| Technology                         | Area of<br>Concern | 2001                          | 2003                                        | 2005                        | 2007                                          | 2013                                                 |

|------------------------------------|--------------------|-------------------------------|---------------------------------------------|-----------------------------|-----------------------------------------------|------------------------------------------------------|

| Fired Ceramic<br>Resistors on Foil | Materials          | Demonstrable                  | Meets<br>Requirements                       | Meets<br>Requirements       | Meets<br>Requirements                         | Meets<br>Requirements                                |

|                                    | Manufacturing      | Low Yields                    | Low Yields (>1<br>defect/10K<br>components) | Acceptable Yields           | Existing<br>Infrastructures                   | Available<br>Cost-Effective<br>Infrastructure        |

|                                    | Design and Test    | In Development                | Demonstrable                                | Demonstrable                | Common Practice                               | Widespread                                           |

|                                    | Cost               | High                          | Acceptable                                  | Competitive                 | Cost Savings                                  | Cost Savings                                         |

|                                    | Availability       | Few Suppliers<br>No Standards | More Suppliers<br>IPC Standards             | Existing<br>Infrastructures | Available<br>Cost-Effective<br>Infrastructure | Standard Parts<br>Available from<br>Multiple Sources |

Table 16: GAP Analysis for Fired Ceramic Resistors on Foil:

Manufacturing experience, and manufacturing infrastructure and the same design and test problems as the singulated capacitors and resistors remain as gaps.

# REFERENCES

- 1. P. A. Sandborn, B. Etienne, and G. Subrananian, "Application Specific Economic Analysis of Integral Passives I Printed Circuit Boards", To be published IEEE Trans. Electronics Packaging Manufacturing

- R.T.Croswell, Savic, M. Zhang, A. Tungare, J. Herbert, K. Noda, P. Tan, and W. Bauer, "Embedded Mezzanine Capacitor Technology for Printed WiringBoards," presented at the IPC Printed Circuit Expo, Long Beach, CA, March 25-28, 2002. This article is reprinted in the trade journal Circuitree, 15 (8), p. 48 (2002).

- 3. George Korony, et.al. "Controlling Capacitor Parasitics for High Frequency Decoupling", Proceedings 2001 IMAPS: October 9-11,2001

# CONTRIBUTORS TO THE NEMI 2002 ROADMAP

# **Passives Components – Chapter Contributors**

| Chairman: Larry Marcanti<br>Co-Chair: Joseph Dougherty<br>John Galvagni<br>Bill Borland<br>Percy Chinoy<br>Robert Croswell | Nortel Networks<br>Penn State University<br>AVX<br>DuPont Microcircuit Materials<br>Shipley<br>Motorola Labs |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Dennis DeBord<br>John Felten                                                                                               | Nortel Networks<br>DuPont Microcircuit Materials                                                             |

| Kim Fjeldsted                                                                                                              | ESI                                                                                                          |

| Dennis Fritz                                                                                                               | MacDermid Inc                                                                                                |

| Bob Greenlee                                                                                                               | Merix                                                                                                        |

| John Jorgensen                                                                                                             | CAL Microdevices                                                                                             |

| Kalvin Korpela                                                                                                             | Nortel Networks                                                                                              |

| Bonnie Larson                                                                                                              | ESI                                                                                                          |

| Joel Peiffer                                                                                                               | 3M                                                                                                           |

| Tom Reynolds                                                                                                               | Murata                                                                                                       |

| Peter Sandborn                                                                                                             | University of Maryland                                                                                       |

| Virang Shah                                                                                                                | MicroFab                                                                                                     |

| Robert Sheffield                                                                                                           | Nortel Networks                                                                                              |

| Matt Snogren                                                                                                               | Coretec / SAS                                                                                                |

| Ken Snowdon                                                                                                                | Nortel Networks                                                                                              |

| John Stankus                                                                                                               | Nortel Networks                                                                                              |

| Richard Ulrich                                                                                                             | University of Arkansas                                                                                       |

| Jiming Zhou                                                                                                                | Delphi Automotive Systems                                                                                    |

|                                                                                                                            |                                                                                                              |